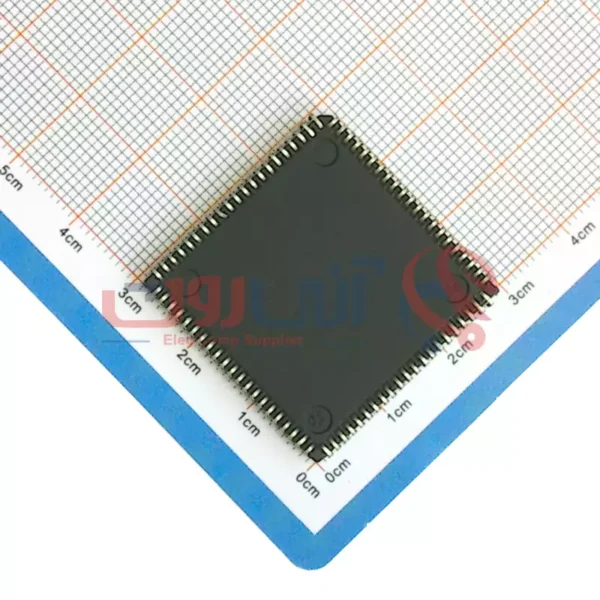

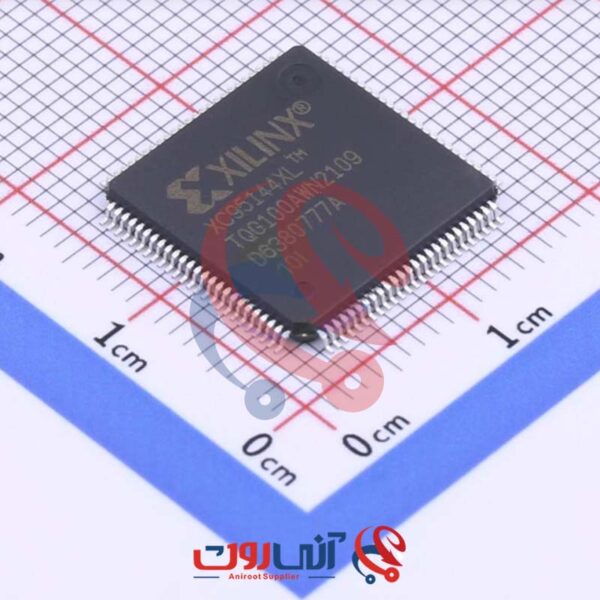

XC2S100TQ144-5I

300,000 تومان

Xilinx Spartan-II 2.5V FPGA

1 عدد در انبار

Spartan-II FPGA

Features

• Second generation ASIC replacement technology

– Densities as high as 5,292 logic cells with up to 200,000 system gates

– Streamlined features based on Virtex® FPGA architecture

– Unlimited reprogrammability

– Very low cost

– Cost-effective 0.18 micron process

• System level features

– Select RAM™ hierarchical memory:

· 16 bits/LUT distributed RAM

· Configurable 4K bit block RAM

· Fast interfaces to external RAM

– Fully PCI compliant

– Low-power segmented routing architecture

– Full readback ability for verification/observability

– Dedicated carry logic for high-speed arithmetic

– Efficient multiplier support

– Cascade chain for wide-input functions

– Abundant registers/latches with enable, set, reset

– Four dedicated DLLs for advanced clock control

– Four primary low-skew global clock distribution nets

– IEEE 1149.1 compatible boundary scan logic

• Versatile I/O and packaging

– Pb-free package options

– Low-cost packages available in all densities

– Family footprint compatibility in common packages

– 16 high-performance interface standards

– Hot swap Compact PCI friendly

– Zero hold time simplifies system timing

• Core logic powered at 2.5V and I/Os powered at 1.5V, 2.5V, or 3.3V

• Fully supported by powerful Xilinx® ISE® development system

– Fully automatic mapping, placement, and routing

محصولات مرتبط

XC2C64A-7VQG44C XILINX

2 عدد در انبار

AMD/XILINX XC2C64A-7VQG44C

Description: VQFP-44(10x10) FPGAs (Field Programmable Gate Array)

Integrated Circuits (ICs)/Embedded

DATA SHEET: XC2C64A-7VQG44C.Pdf

EPM3064ATC44-10N Altera

2 عدد در انبار

Intel/Altera EPM3064ATC44-10N

Description: TQFP-44(10x10) FPGAs (Field Programmable Gate Array)

Integrated Circuits (ICs)/Embedded

DATA SHEET: EPM3064ATC44-10N.Pdf

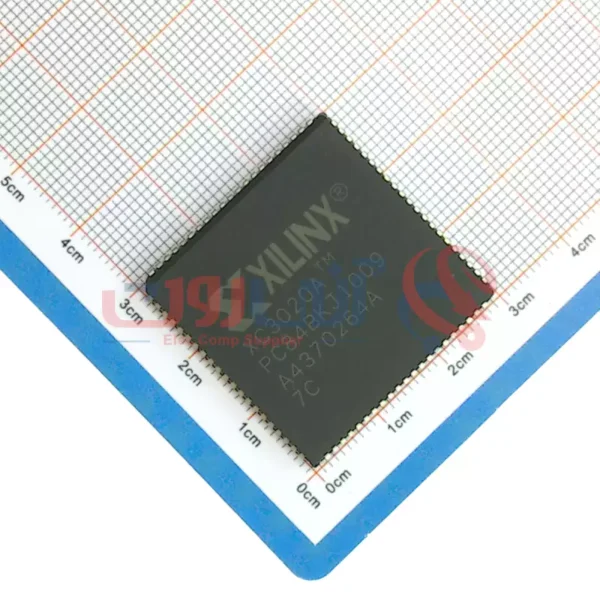

XC3020A 7PC84C renew XILINX

8 عدد در انبار

XC95144XL-10TQG144I

برای سفارش تماس بگیرید.

نقد و بررسیها

هنوز بررسیای ثبت نشده است.